パッケージ寄生パラメータを抑えることにより電力損失を削減、高周波動作で高効率を実現

パッケージ寄生パラメータを抑えることにより電力損失を削減、高周波動作で高効率を実現

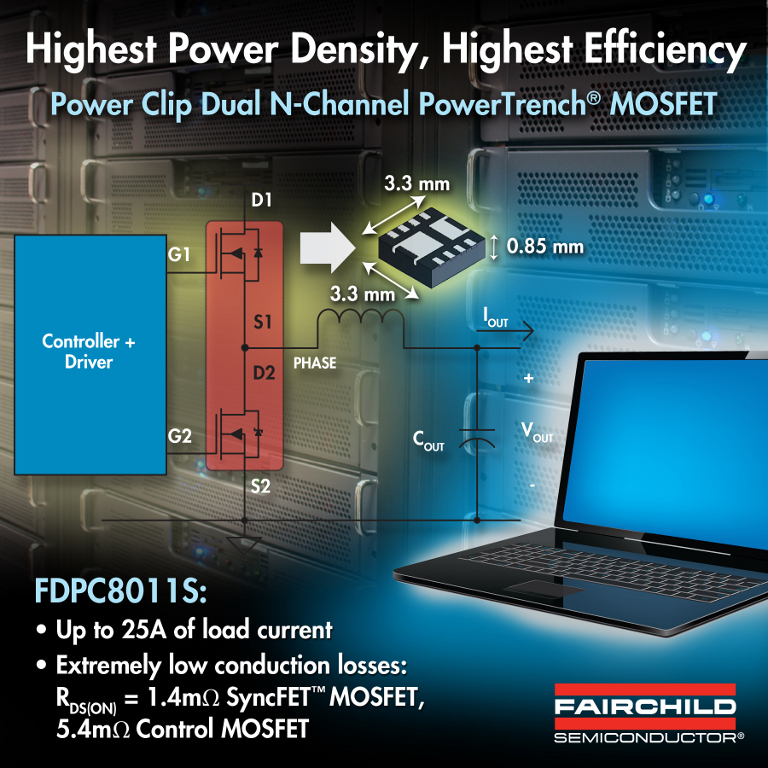

2012年5月24日 – 高密度・組込み型DC-DC電源において機能の充実に伴いより大きな出力が要求されるに従って、電源回路設計者には小さなスペースでより高い電力密度および高効率の実現が求められます。このようなシステム要求の実現を支援するためフェアチャイルドセミコンダクタージャパン㈱(本社:東京都渋谷区、社長:雨宮隆久)は、25V、3.3×3.3mm2、薄型パワークリップ・パッケージ採用の非対称デュアルNチャネルモジュールFDPC8011Sを発表しました。

FDPC8011Sはより高速のスイッチング周波数で動作するよう開発されており、ローサイドに1.4mΩ SyncFET™、ハイサイドに低FOM(性能指数)5.4mΩ NチャネルMOSFETを用いて構成され、オールクリップ・パッケージに統合されています。この結果、降圧同期整流アプリケーションにおいてインダクタサイズの小型化及びコンデンサの個数削減に寄与します。デバイスのローサイド側はソースダウン技術採用により部品の配置・配線を容易にし、コンパクトな基板レイアウトが可能になり、最適の放熱特性が得られます。FDPC8011Sは25Aを超える出力電流に対応し、従来からある他の3x3mm2 デュアル MOSFETに比べ出力電流能力は2倍になっています。

特長と利点

- Nチャネル・コントロール(ハイサイド)MOSFET:

オン抵抗RDS(ON) = 5.4mΩ_typ (7.3mΩ_max) @VGS = 4.5V - Nチャネル・シンクロナス(ローサイド)MOSFET:

オン抵抗RDS(ON) = 1.4mΩ_typ (2.1mΩ_max) @VGS = 4.5V - 低インダクタンス・パッケージ採用で立上がり/立下り時間を削減、その結果、スイッチング損失が減少

- MOSFETを統合することで最適なレイアウトが可能、 回路インダクタンス及びスイッチノードのリンギングを抑制

- RoHS対応

より詳細な製品情報は下記サイトをご覧下さい:

http://www.fairchildsemi.com/pf/FD/FDPC8011S.html

3.3×3.3mm2パワークリップ非対称Nチャネル・デュアルMOSFETはフェアチャイルドの広範囲な高性能MOSFETテクノロジーの一部であり、高効率で故障の許されない情報処理設計に携わるパワー設計者に幅広いソリューションを提供します。

価格:

1.60ドル(1,000個購入時)

入手性:

サンプル出荷中

量産納期:

8-12週間

製品の各種資料はこちらをご参照ください。

データシート

http://www.fairchildsemi.com/ds/FD/FDPC8011S.pdf